HyperSPARC

From Wikipedia, the free encyclopedia

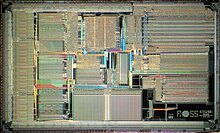

hyperSPARC (ハイパースパーク)は、コードネーム「Pinnacle」と呼ばれ、サイプレス・セミコンダクターグループのROSSテクノロジ社が開発したSPARCバージョン8命令セットアーキテクチャ(ISA)を実装したマイクロプロセッサ。

hyperSPARCは、1993年に市場投入され、サン・マイクロシステムズのSuperSPARCと競合した。マイクロアーキテクトは、ラジュ・ベゲスナだった。 hyperSPARCは、1990年代半ばのサン・マイクロシステムズ社の主要な競合製品のひとつだった。富士通がサイプレス社からROSS社を買収したとき、hyperSPARCは、富士通の子会社であるHALコンピュータシステム社が開発したSPARC64よりも重要な存在になると考えられ、アナリストにもこの考え方が共有された。

形状

hyperSPARCは、双方向のスーパースカラーマイクロプロセッサだった。整数ユニット、浮動小数点ユニット、ロード/ストアユニット、ブランチユニットの4つの実行ユニットがあった。 hyperSPARCにはオンダイの8KB命令キャッシュがあり、そこからサイクルごとに2つの命令がフェッチされ、デコードされる。デコーダは、以前にデコードした命令が実行ユニットに発行されていなければ、新しい命令をデコードできなかった。

整数レジスタファイルには136個のレジスタが含まれ、SPARC ISAで定義された機能である8個のレジスタウィンドウを提供する。読み取りポートは2つある。整数ユニットには4ステージのパイプラインがあり、そのうち2ステージが追加されたため、パイプラインはすべての非浮動小数点パイプラインと等しくなる。整数の乗算と除算、SPARCアーキテクチャのV8バージョンで追加された命令は、それぞれ18サイクルと37サイクルのレイテンシを持ち、完了するまでパイプラインを停止させた。

このマイクロプロセッサは、MBusシステム上でのマルチプロセッシングをサポートしていた。

hyperSPARCは120万個のトランジスタで構成されている。サイプレス社が0.65 µm、2層金属、CMOSプロセスで製造した。hyperSPARCの後継では、新機能によりトランジスタが増えたため、新しいプロセスに移植された。NECが製造した最後の工程を除いては、富士通が製造を行った。

パッケージ

hyperSPARCはマルチチップデザインであった。これは、ピングリッドアレイ(PGA)を備えた、セラミック製のマルチチップモジュール(MCM)にパッケージ化されていた。